编辑:Helan 发布:2016-06-29 15:18

三星公司已经开始量产其48层(即单NAND内48层单元,属于第三代升级技术)3D V-NAND芯片,预计其将被用于SSD T3(mSATA接口加850 EVO V2)、NVMe SSD(PM971-NVMe)以及企业级SSD(PM1633a)等SSD产品。在各设备当中,将包含大量48层3D V-NAND存储芯片且通过引线键合技术实现彼此堆叠。三星公司在48层3D V-NAND芯片中集成了512 GB存储单元,意味着每个NAND芯片为32 GB容量(256 Gb)。三星的32层(第二代方案)3D V-NAND芯片则为10.67 GB容量(85.33 Gb)。因此,第二代与第三代3D V-NAND设备之间到底存在哪些差别?是否单纯只是将单元层数由32提升到48?

对此,我们对两款设备进行深入剖析,着眼于单元架构、材质、布局以及封装等角度。下面来看分析结论:

存储密度与芯片平面图

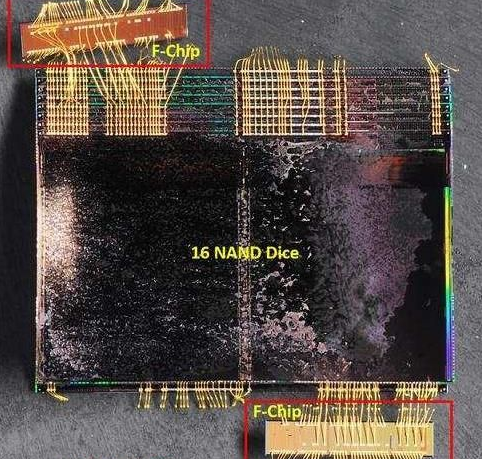

图一所示为16 48层3D V-NAND芯片,MCP(即多芯片封装)内包含双F-Chips。48层的裸片效率显然更高。32层3D V-NAND芯片面积为84.3平方毫米,而48层3D V-NAND芯片则为99.8平方毫米,意味着其长度较上代方案提升17.3%(如图二所示)。每单元芯片存储密度则提升至2.57 Gb每平方毫米。而目前最顶级的高密度2D平面NAND设备为东芝的15纳米TLC NAND,具体水平为1.28 Gb每平方毫米。二者之间的最大差异在于:1)平面(NAND存储阵列)区,2)位线开关与页缓冲区,3)逻辑与外围区以及4)加入F-Chips。每块芯片分为两层。NAND存储阵列区由原本的48.9平方毫米增加至68.7平方毫米,提升为40.3%。而位线开关电路则与32层方案保持一致,不过页面缓冲区则缩小了20%。逻辑与外围电路面积减少34.8%。换言之,三星方面大幅削减了页缓冲与周边区面积,从而使其在存储密度与芯片效率方面得到提升。另外,16层堆叠设计中的芯片厚度也由132微米降低至36微米。

图一,三星48层3D V-NAND设备,采用16层垂直堆叠NAND芯片与双F-Chips,拆机图片。

图二,32层与48层3D V-NAND对比。

F-Chip闪亮登场

三星公司在去年的ISSCC2015大会上首公宣布将F-Chip嵌入至其NAND闪存封装当中。总体来讲,SSD硬件架构是由存储控制器、NAND闪存与DRAM所共同构成。

F-Chip负责在存储控制器之间的I/O总线上实现点对点拓扑,另外F-Chip还会对通道内的不必要反射进行缓冲。另外,F-Chip在其与NAND设备之间建立了两套内部I/O总线,从而降低F-Chip到NAND接口的容量负载。另外,其支持再定时模式,旨在从存储控制器中将I/O信号传输至NAND设备。

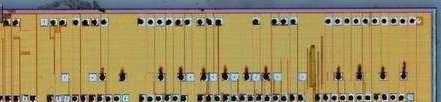

再有,F-Chip亦改善了NAND设备与异步接口中出现的时序容限所引发的定时不稳状况。单一F-Chip接入八块V-NAND芯片,意味着双F-Chips可嵌入至16芯片封装内。图三所示为从MCP中分离出来的F-Chip,其中包含ROM、DC发电、CMD译码器、数据路径、TX/RX以及引线接合盘等电路元件。F-Chip芯片面积为0.057平方毫米。

图三,从三星48层3D V-NAND MCP中拆分出来的F-Chip芯片。

存储单元阵列结构与架构

相较于第二代32层3D V-NAND,第三代48层3D V-NAND单元结构拥有更高单元门数量,这意味着进程整合所带来的要求与控制性将更具挑战。硅通孔与CSL(即公共源线)沟槽蚀刻工艺的长宽比约为33比26,高于32层3D V-NAND设备。另外其采用基于铝质材料的高k介质电阻挡层以及CTF(电荷捕获闪存存储)或者CTL(电荷捕获层)。

选择晶体管则包括SSL(串选择线)与GSL(接地选择线),拟栅极与位线带设计与上代方案保持一致,不过SEG(硅外延延伸)高度则得以削减。32层3D V-NAND设备拥有三金属层,而48层3D V-NAND则拥有四金属层。额外的这一金属层(通常被称为M0)被添加至CSL/MC层上,这可能是为了进一步提升单元设计效率。

成本考量:1y纳米2D与48层3D V-NAND

对于16纳米或15纳米的1y级别MLC/TLC NAND设备,其制程整合在存储单元阵列与周边区域之上,包括阱/活动/隔离(SA-STI,自对准STI)形式;单元FG/CG与外围门形式;以及接触与互连(金属与通孔)形式。当然,DPT(双图案化技术)或者QPT(四图案化技术)等图案化方案以及气隙制程实现活动、字线与位线模式的作法也存在于2D平面NAND产品的制造流程当中。对于1y纳米级别的2D平面NAND设备,NAND制造商往往会使用40到45个掩模层,意味着其需要40到45次光刻步骤才能将设备集成在硅晶圆之上。

另一方面,32层3D V-NAND设备则采用垂直硅通孔技术(简称CHT)与20纳米位线半间距(配合DPT),意味着其需要50层掩模以反复调整具体图案,从而保证存储阵列周边位置的通孔能够使各层确切连接。尽管48层3D V-NAND的存储单元结构/材质与单元设计同32层3D V-NAND一样,但更高的门堆叠数量与蚀刻步骤会给吞吐量、良品率及产量控制带来难题。随着各大主流NAND厂商积极投入于48层、64层、96层甚至是128层3D NAND产品制造并持续提升产量,相信NAND存储方案的使用成本将通过3D NAND架构的规模扩展而不断降低。

未来NAND闪存存储技术

相信未来几年中,2D设备将与3D NAND并行存在。然而,2D NAND的制程工艺已经基本达到了极限,且三星、东芝、SanDisk、美光、英特尔以及SK-海力士等主流厂商都开始探索利用通孔机制将多层NAND构成3D形式。一旦可堆叠的单元门数量进一步提升,则有望带来更高存储密度、更强性能、更理想的可靠性以及更低功率水平。截至目前,三星32层与48层3D V-NAND产品与美光/英特尔32层3D NAND产品已经正式投放商业市场。

东芝、SanDisk与SK-海力士的3D NAND设备尚未全面发布,意味着其在迈入3D NAND主流厂商的道路上显得有些迟钝。三星公司的顶级32层与48层3D V-NAND设备基于电荷捕捉闪存(简称CTF)存储架构(或者电荷捕捉层,简称CTL),配备有高k介质阻挡层与金属门。CTL属于非导电层,采用氮化物等材质充当绝缘体,并配合其它存储单元功能以降低单元之间的干扰,从而控制错误数量并提升可靠性。由于 3D V-NAND单元对单元间干扰并不敏感,因此能够显着提升数据写入速度,从而带来更理想的性能。其制程步骤数量已经大大降低,且功耗水平也因此得到有效控制。48层3D NAND在使用成本曲线上较32层方案更接近2D闪存。而未来几年内可能陆续推出的64层、96层甚至是128层3D NAND则可能受到多晶硅沟槽迁移率、光蚀刻加工能力以及良品率/产量控制等因素的影响而导致产能不高。

那么现在让我们回归最初的疑问:三星48层3D V-NAND是否只是对32层方案的单纯垂直扩展?答案是否定的。除了垂直扩展,新一代技术还提升了单元性能效率,嵌入F-Chip并将逻辑与周边区面积降低30%以上,同时添加新的金属层以提升芯片效率。很明显,3D V-NAND已经开始全面迎来成熟期。

| 存储原厂 |

| 三星电子 | 53700 | KRW | +1.32% |

| SK海力士 | 169800 | KRW | +0.77% |

| 铠侠 | 1594 | JPY | -6.51% |

| 美光科技 | 90.120 | USD | +3.48% |

| 西部数据 | 60.240 | USD | +1.04% |

| 南亚科 | 31.00 | TWD | +1.97% |

| 华邦电子 | 15.20 | TWD | +1.33% |

| 主控厂商 |

| 群联电子 | 479.5 | TWD | +3.34% |

| 慧荣科技 | 53.900 | USD | +1.26% |

| 联芸科技 | 43.78 | CNY | +2.17% |

| 点序 | 45.30 | TWD | +0.67% |

| 国科微 | 72.23 | CNY | -1.90% |

| 品牌/模组 |

| 江波龙 | 94.22 | CNY | -1.09% |

| 希捷科技 | 87.310 | USD | -0.26% |

| 宜鼎国际 | 214.5 | TWD | +1.90% |

| 创见资讯 | 90.3 | TWD | +1.46% |

| 威刚科技 | 79.0 | TWD | +0.13% |

| 世迈科技 | 18.510 | USD | +0.82% |

| 朗科科技 | 22.05 | CNY | -3.42% |

| 佰维存储 | 66.03 | CNY | -2.38% |

| 德明利 | 90.40 | CNY | -2.16% |

| 大为股份 | 12.56 | CNY | -3.98% |

| 封测厂商 |

| 华泰电子 | 34.60 | TWD | +1.76% |

| 力成 | 124.5 | TWD | +2.47% |

| 长电科技 | 39.14 | CNY | -2.10% |

| 日月光 | 160.5 | TWD | +1.90% |

| 通富微电 | 29.36 | CNY | -2.72% |

| 华天科技 | 11.93 | CNY | -2.21% |

深圳市闪存市场资讯有限公司 客服邮箱:Service@ChinaFlashMarket.com

CFM闪存市场(ChinaFlashMarket) 版权所有 Copyright©2008-2023 粤ICP备08133127号-2