编辑:Helen 发布:2018-11-06 12:39

3D NAND指的是闪存芯片的存储单元是 3D 的。此前的闪存多属于平面闪存 (Planar NAND),而3D NAND,顾名思义,即是指立体结构的闪存。如果平面闪存是平房,那 3D NAND 就是高楼大厦。把存储单元立体化,意味着每个存储单元的单位面积可以大幅下降。下图为三星Planar NAND 发展至 3D NAND (V-NAND) 的示意图。

.jpg)

图片来源 : 三星V-NAND technology White Paper (Modified by Author)

左边二个是 Planar NAND,只是存储单元结构不同,由浮动栅结构 (Floating Gate) 迁移至电荷撷取闪存,即上图中的 2D CTF (Charge Trap Flash)。然后是将 2D CTF 存储单元 3D 化变成 3D CTF 存储单元 (上图的 3D CTF),最后通过工艺技术提升逐渐往上增加存储单元的层数(Layer ),把存储单元像盖大楼一样越做越多层。三星的 3D V-NAND 存储单元的层数 (Layer) 由 2009 年的 2-layer 逐渐提升至 24-layer、64-layer,今年已经达到 96-layer。

图片来源 : 三星V-NAND technology White Paper (Modified by Author)

近几年来国际原厂先后投入 3D NAND 研发。各家的 3D NAND 存储单元及技术都不相同,也几乎每家公司都已宣布开发出 96 层 3D NAND。

多层单元 (Multi-Level Cell)

一般正常的存储单元,不管是 DRAM、SRAM、FLASH、ROM 等等,都只存储一个比特 (Bit) 的资料 (称为 SLC,Single-Level Cell)。为能更缩小存储单元尺寸,除了运用工艺持续做小及将存储单元 3D 化外,各厂商也积极思考增加每存储单元能存储的 bit 数目。当一个存储单元可以存储二个 bit 时 (称为 MLC,Multi-Level Cell),其存储单元尺寸等同于减少一半 ; 存储三个 bit (称为 TLC,Triple-Level Cell),则尺寸等同于原有的 1/3 ; 四个 bit (称为 QLC,Quad-Level Cell),则存储单元尺寸只剩原有的 1/4。

SLC 存储一个 bit 数据,也就是二个状态 (0,1) ; MLC 存储二个 bit 数据,所以是四个状态 (00,01,10,11) ; TLC 三个 bit,八个状态 (000,001,010,011,100,101,110,111) ; QLC 四个 bit,十六个状态 (0000,0001,…. 1111),如下图所示。

图片来源 : Micron Official Website (Modified by Author)

天下没有白吃的午餐,鱼与熊掌不可兼得,存储单元尺寸降低的代价是设计难度的提高以及性能的降低。为什么会如此?又是一个简单的算数问题。假设存储单元电压是 1.8V,对 SLC 而言,一个 bit 有二个状态,平均分配 1.8V 电压,每个状态可以分到 0.9V。对 MLC 而言,四个状态平均分配电压,每个状态可以分到 0.45V,以此类推,TLC 每个状态只可以分到 0.225V,而 QLC 更惨,每个状态只可以分到 0.1125V。在这么小的电压下,这么多的状态以极小的电压区隔,电压区隔越小越难控制,干扰也越复杂,而这些问题都会影响 TLC 或 QLC 闪存的性能、可靠性及稳定性。

如上图所示,越往右,存储单元相对尺寸越小,因而成本越低。但其编程/擦除周期 (Program/Erase Cycle,简称 P/E Cycle,也有人称为擦写次数) 会大幅降低,同时读、写及擦除所需的时间也会增加 (性能降低)。擦写次数的降低为这项技术带来相当大的争议,因为擦写次数代表这闪存的寿命长短。如同上图所示,从 SLC 到 QLC,擦写次数由 10 万次降到只有1000次。

原厂采用系统设计来弥补这项缺点。通过系统控制平均分摊每一个区块的擦写次数,故障的区块也会被尚未使用的区块替换,以确保了闪存能持续运行。即使每个存储单元只有1000次擦写次数,整颗闪存仍然可以从容的应付我们日常使用的需求。当然,这样的结果使得 TLC 或 QLC 只适用于消费者个人使用 (例如 SSD),它是无法满足 Data Center 之类的企业需求的,因为商用,例如资料处理中心 (Data Processing Center),的存储设备,其擦写频率是相当相当高的。

硅穿孔技术 (TSV,Through Silicon Via)

硅穿孔技术其实与 3D NAND 工艺无关,严格来说,它属于一种封装技术。会拿出来讲主要是一方面它可让 3D NAND 闪存更上层楼,容量加大好几倍。另一个原因是因为有些人把它跟 3D NAND 存储单元的 layer 层数混淆了,他们把 32、64 或 96-layer 3D NAND 描述为把 32、64 或 96 个晶粒 (Die) 堆叠在一起,这是很大的误解。

TSV 技术已普遍用于 DRAM及 Flash 产品。以往一个 IC 芯片 (Chip) 只封装一颗晶粒,渐渐地为了降低成本、节省主机板空间及提高性能,多芯片封装 (MCP,Multi-Chip Package) 开始盛行 (如下图左方图示)。TSV 则是以工艺方式将 IC 基板 (Substrate) 穿孔,填入金属,让上下晶粒直接相导通 (如下图右方图示),不仅省去像左方图示所显示封装打线 (Bonding),更能进一步提升 DRAM 或 Flash 单颗芯片的容量、讯号品质、传输性能,以及降低传导杂讯干扰。

图片来源 : 3D NAND Flash Memory - Toshiba (Modified by Author)

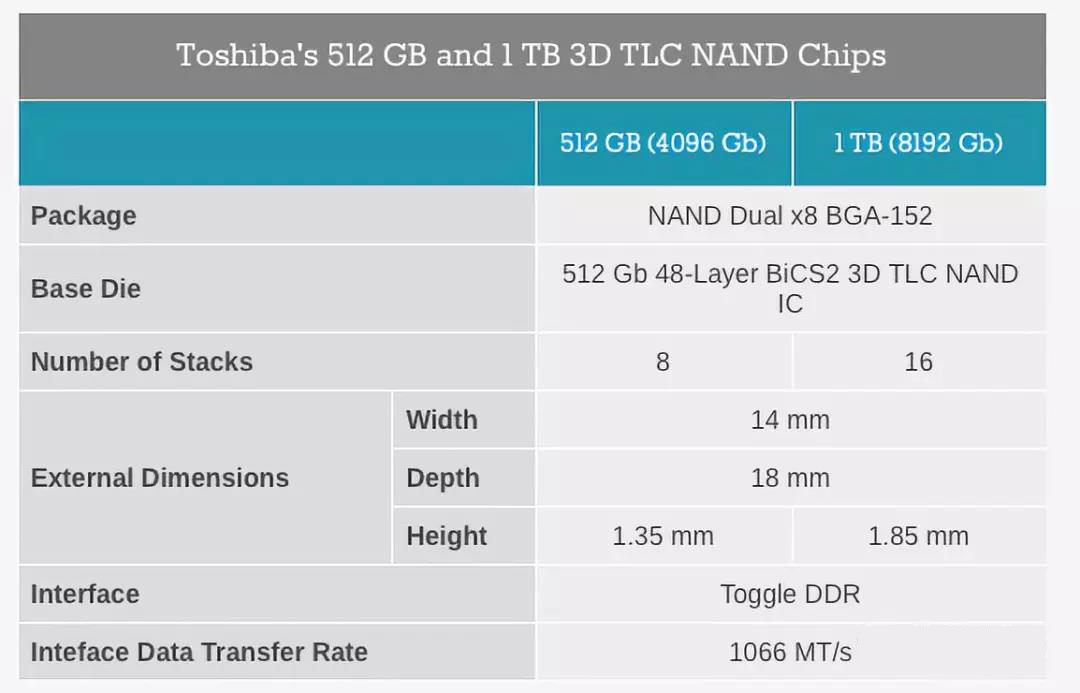

目前各家量产的 3D NAND 芯片大多只以 TSV 堆叠到 8 或 16 层 3D NAND 晶粒 (Die)。下表范例为东芝的 512GB (Gigabyte)/1TB (Terabyte) 闪存产品介绍,你可以清楚看到它使用 48-layer 的 3D NAND 存储工艺制造出容量为 512 Gb (Gigabit) 的闪存晶粒,再以 TSV 技术分別堆叠 8 或 16 个 die (在下表中是以 Number of Stacks 来表示堆叠数目) 来做出 512 GB (512Gb x 8) 或 1TB (512Gb x 16) 的闪存芯片。(注 : 小写的 b 代表 bit (比特),大写 B 代表 byte (字节),一个 byte 等于 8 个 bits)。

图片来源 : AnandTech Post : Toshiba Weds 3D NAND and TSV

所以,一个 NAND 闪存的晶粒 (die),运用 3D NAND 技术,可以把多达 96-layer 的存储单元堆叠在一起,像盖摩天大楼一样。而为了增加每个封装芯片 (Chip) 的容量,厂商再把8个或16个晶粒 (die) 以TSV 的技术叠在一起去封裝成芯片。

| 存储原厂 |

| 三星电子 | 53500 | KRW | +0.94% |

| SK海力士 | 170400 | KRW | +1.13% |

| 铠侠 | 1597 | JPY | -6.33% |

| 美光科技 | 90.120 | USD | +3.48% |

| 西部数据 | 60.240 | USD | +1.04% |

| 南亚科 | 31.00 | TWD | +1.97% |

| 华邦电子 | 15.20 | TWD | +1.33% |

| 主控厂商 |

| 群联电子 | 479.5 | TWD | +3.34% |

| 慧荣科技 | 53.900 | USD | +1.26% |

| 联芸科技 | 44.39 | CNY | +3.59% |

| 点序 | 45.30 | TWD | +0.67% |

| 国科微 | 72.29 | CNY | -1.82% |

| 品牌/模组 |

| 江波龙 | 94.44 | CNY | -0.86% |

| 希捷科技 | 87.310 | USD | -0.26% |

| 宜鼎国际 | 214.5 | TWD | +1.90% |

| 创见资讯 | 90.3 | TWD | +1.46% |

| 威刚科技 | 79.0 | TWD | +0.13% |

| 世迈科技 | 18.510 | USD | +0.82% |

| 朗科科技 | 22.00 | CNY | -3.64% |

| 佰维存储 | 66.35 | CNY | -1.91% |

| 德明利 | 91.05 | CNY | -1.46% |

| 大为股份 | 12.60 | CNY | -3.67% |

| 封测厂商 |

| 华泰电子 | 34.60 | TWD | +1.76% |

| 力成 | 124.5 | TWD | +2.47% |

| 长电科技 | 39.08 | CNY | -2.25% |

| 日月光 | 160.5 | TWD | +1.90% |

| 通富微电 | 29.40 | CNY | -2.58% |

| 华天科技 | 11.94 | CNY | -2.13% |

深圳市闪存市场资讯有限公司 客服邮箱:Service@ChinaFlashMarket.com

CFM闪存市场(ChinaFlashMarket) 版权所有 Copyright©2008-2023 粤ICP备08133127号-2